DATAMATH CALCULATOR MUSEUM

|

DATAMATH CALCULATOR MUSEUM |

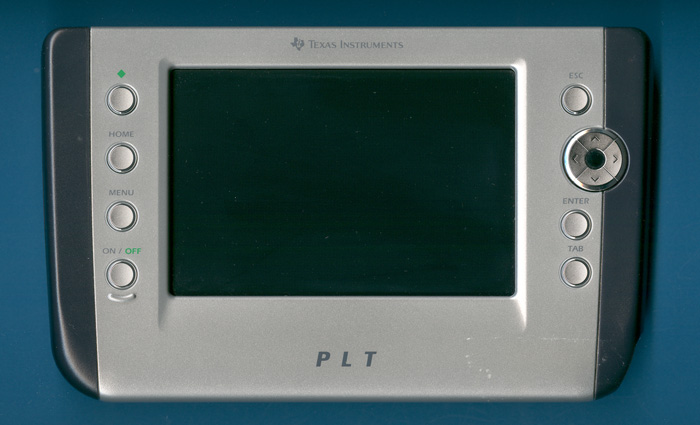

Texas Instruments Personal Learning Tool PLT SU1

| Date of introduction: | never | Display technology: | LCD Color dot matrix |

| New price: | Display size: | 480 * 320 pixels | |

| Size: | 5.1" x 8.1" x 1.1" 130 x 207 x 29 mm³ |

||

| Weight: | 20.6 ounces, 586 grams | Serial No: | PTR 1261 |

| Batteries: | Li-Ion PLT BAT1 | Date of manufacture: | year 2003 |

| AC-Adapter: | AC9926 | Origin of manufacture: | Taiwan (I) |

| Precision: | Integrated circuits: | CPU: TI OMAP5910 SDRAM: Samsung K4M56163P Flash: Toshiba TC58DVM82A, Fujitsu 29LV400TC |

|

| Memories: | |||

| Program steps: | 16M Bytes SDRAM, 512k Bytes NOR Flash ROM, 32M Bytes NAND Flash-ROM | Courtesy of: | Texas Instruments |

![]()

The Datamath Calculator Museum received this unique graphing calculator as a loan from Texas Instruments in February 2008 to photograph and document it.

The Datamath Calculator Museum received this unique graphing calculator as a loan from Texas Instruments in February 2008 to photograph and document it.

We learned from Texas Instruments that they developed a family of next-generation Personal Learning Tool products based on the LINUX operating system. The Dallas, TX based team nicknamed

it PET Project and we know:

We learned from Texas Instruments that they developed a family of next-generation Personal Learning Tool products based on the LINUX operating system. The Dallas, TX based team nicknamed

it PET Project and we know:

| •

PLT SHH1: Spot Hand Held, first generation PET device with smaller, portrait oriented screen. • PLT FHH1: Fido Hand Held, first generation PET device with larger, landscape oriented screen • This PLT SU1 is actually a second generation PET device with a large color screen with roughly the size of the previous PLT FHH1. |

The backside of the wonderful designed calculator carries a nice, handwritten label:

Toto Pilot Build. We immediately remember the famous children’s novel The Wonderful Wizard of

Oz, published in 1900 and the dog of Dorothy Gale.

The backside of the wonderful designed calculator carries a nice, handwritten label:

Toto Pilot Build. We immediately remember the famous children’s novel The Wonderful Wizard of

Oz, published in 1900 and the dog of Dorothy Gale.

Removing the foldable stand on the back of the calculator displays the product information:

Model No: PLT - SU1, © 2003, Made in Taiwan.

Removing the foldable stand on the back of the calculator displays the product information:

Model No: PLT - SU1, © 2003, Made in Taiwan.

Comparing the PLT SU1 with the earlier PLT FHH1 reveals some differences:

| •

Up-to-date, very valuable looking design • Seven keys plus cursor control instead the previous eight keys and cursor control. • Much larger battery • Different slots for external connectivity • Color touch-screen instead of the previous monochrome touch-screen |

Architecture: Dismantling the PLT SU1 reveals a modern architecture based on the OMAP architecture introduced by Texas Instruments already in 2001 very similar to the PLT SHH1 and PLT FHH1. Learn more about the

Hardware Architecture of TI’s Graphing Calculators. The different memory chips used in this Engineering Samples promised an unbelievable huge workspace of 24M Bytes and even an additional slot for a SD Memory Card. In addition we recognized an unknown Philips CA4885 device which is probably responsible for the power supply.

Architecture: Dismantling the PLT SU1 reveals a modern architecture based on the OMAP architecture introduced by Texas Instruments already in 2001 very similar to the PLT SHH1 and PLT FHH1. Learn more about the

Hardware Architecture of TI’s Graphing Calculators. The different memory chips used in this Engineering Samples promised an unbelievable huge workspace of 24M Bytes and even an additional slot for a SD Memory Card. In addition we recognized an unknown Philips CA4885 device which is probably responsible for the power supply.

Processor: The first-generation OMAP™ 5910 combines in one system the TMS320C55x DSP (Digital Signal Processor) with a ARM925 RISC (Reduced Instruction Set Computing) to perform the perfect balance between performance and power consumption for mobile products. While the OMAP™ 1510 used in the earlier PLT SHH1 and PLT FHH1 was developed for PDAs (Personal Digital Assistants) and smartphones, the OMAP™ 5910 was intended for internet appliances and web pads.

Processor: The first-generation OMAP™ 5910 combines in one system the TMS320C55x DSP (Digital Signal Processor) with a ARM925 RISC (Reduced Instruction Set Computing) to perform the perfect balance between performance and power consumption for mobile products. While the OMAP™ 1510 used in the earlier PLT SHH1 and PLT FHH1 was developed for PDAs (Personal Digital Assistants) and smartphones, the OMAP™ 5910 was intended for internet appliances and web pads.

Memory: The PLT SU1 makes use of three different memory chips:

Memory: The PLT SU1 makes use of three different memory chips:

| •

NOR Flash-ROM • NAND Flash-ROM • SDRAM |

Flash memory is non-volatile and does not need a battery to maintain the information stored in the chip. In the past years two different technologies emerged in parallel with some advantages and disadvantages.

The NOR Flash-ROM was invented by Toshiba in 1984 and found its way immediately as a replacement of the more expensive ROM (NRE mask costs) and EEPROM (device costs) memory. The NOR Flash-ROMs use an address and data bus to allow the random access to any memory location. Main disadvantages of the NOR Flash-ROM compared to the NAND Flash-ROM are the higher costs, larger housings and slower write speeds.

The disassembled PLT SU1 (Manufactured 2003) makes use of one 29LV400TC, manufactured by Fujitsu, Japan with a 256k*16 bits organization. We know this chip already from the PLT SHH1 and PLT FHH1.

The NAND Flash-ROM architecture was introduced by Toshiba in 1989 and is based on pages of typically 512 to 2048 Bytes and blocks of typical 32 or 64 pages.

While programming is performed on a page basis, erasure can only be performed on a block basis. NAND Flash-ROMs requires bad block management to be performed by device driver software or hardware. Due to the missing address bus the NAND Flash-ROM chip doesn't allow random access to the individual memory positions and therefore it can't be used for program memory of a microprocessor. Typical use of the NAND Flash-ROM memory is file based mass-memory storage such as memory cards.

The disassembled PLT SU1 makes use of one Toshiba TC58DVM82A NAND EEPROM with 32M Bytes capacity compared with 8M Bytes resp. 16M Bytes of the PLT SHH1 and PLT FHH1.

SDRAM is the abbreviation of synchronous dynamic random access memory and is used as program and data memory for microprocessor systems. Each bit of data in a SDRAM is stored in separate capacitor on the integrated circuit. Since these capacitors leak charge over time, the information eventually fades unless the capacitor charge is refreshed periodically.

Because of this refresh requirement, it is a dynamic memory as opposed to SRAM and other static memory. Its advantage over SRAM is its structural simplicity: only one transistor and a capacitor are required per bit, compared to six transistors in SRAM. This allows SDRAM to reach very high density at low cost. Since SDRAM loses its data when the power supply is removed, it is accompanied usually by a NOR Flash-ROM.

During power-up of the system the program content of the NOR Flash-ROM is simply copied into the SDRAM and executed from there. We assume that the PLT FHH1 uses the SDRAM as workspace for user data but stores changes on them into the NAND Flash-ROM.

The disassembled PLT SU1 makes use of one Samsung K4M56163P SDRAM with 16M*16 bits capacity compared with 8M*16 bits SDRAM located in the PLT SHH1 and PLT FHH1.

Display: The PLT SU1 uses a high-contrast color display with a resolution of 480 * 320 pixels, a huge improvement over the monochrome display used in the PLT FHH1. The large touch-screen display includes a novel split screen capability with up to 4 views.

Display: The PLT SU1 uses a high-contrast color display with a resolution of 480 * 320 pixels, a huge improvement over the monochrome display used in the PLT FHH1. The large touch-screen display includes a novel split screen capability with up to 4 views.

Five components not easily detected on the printed circuit board (PCB) of the display module are the driver circuits of the LC-Display. They are probably bare chips mounted directly to the glass substrate of the LCD module and drive 160 rows resp. columns, each.

Connectivity: The PLT SU1 features a huge variety of connectors to the outside world:

| •

Serial port similar to TI-83 • Slot for PLT WC Wireless Card or PLT IRDA Infrared Communication Card • Expansion Slot (no information available) • Slot for a MultiMediaCard (MMC) • Connector for earphones • USB 2.0 connector (Series A) • USB 2.0 connector (mini USB) • Charger for PLT SU1 battery |

The serial port of the PLT SHH1 and PLT FHH1 was replaced with a miniUSB connector and a new feature is the earphone connectors. Texas Instruments confirmed that the PLT SU1 plays MP3 files! The PLT WC Wireless Card allows the connection to the PLT VIEW Presentation Adapter.

ROM-Versions:

No information available

Texas Instruments

worked secretly on the Phoenix 1 and announced in 2006 the TI-Nspire CAS+, but it took another year before the long-awaited

TI-Nspire

calculator family arrived finally July 2007 in the store shelves.

If you have additions to the above article please email: joerg@datamath.org.

© Joerg Woerner, March 8, 2008. No reprints without written permission.