DATAMATH CALCULATOR MUSEUM

|

DATAMATH CALCULATOR MUSEUM |

Additional Pictures

| The backside

of the TI-Nspire prototype with the serial number B-P3-DVT2.0-1466.

|

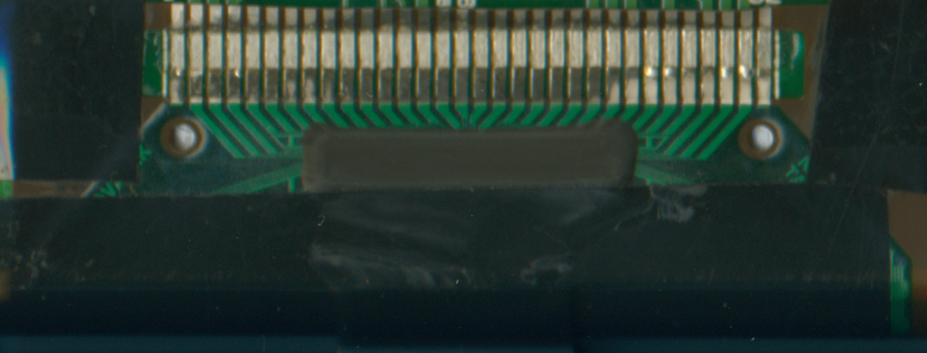

| The internal

construction of the TI-Nspire prototype is close to the final release. The printed circuit board (PCB) of the display was manufactured around February 2007.

|

| The frontside of the

PCB's reveal the construction of the 240 * 320 pixel gray-scale LC-Display and the ARM9 based 32-bit RISC processor.

|

| The brain of the

TI-Nspire is actually a System-on-Chip based on the ZEVIO

architecture from LSI Logic. We assume that the 208 pin housing hosts a 90 MHz ARM9 32-bit RISC processor.

|

| The TI-Nspire uses three

different memory chips, a 256k*16 NOR Flash-ROM, 32M Bytes

NAND Flash-ROM, and 16M*16 SDRAM. The clock frequency of the SoC is 27 MHz.

|

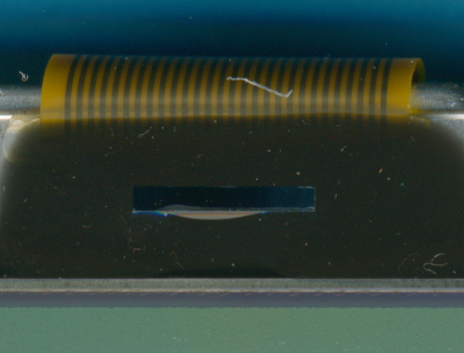

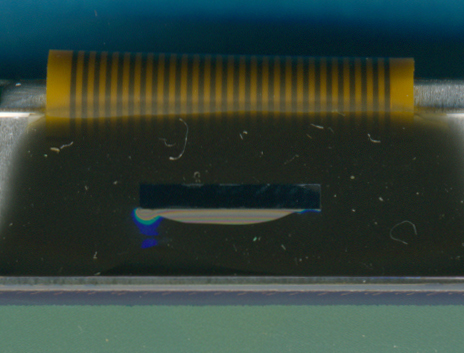

| he 320 * 240 pixel

gray-scale LC-Display needs a total of three drivers. We located this Novatek NT7702 row-driver and two unidentified column-drivers.    |

If you have additions to the above article please email: joerg@datamath.org.

© Joerg Woerner, August 28, 2018. No reprints without written permission.